Technical Program 2025

How to View Abstracts:

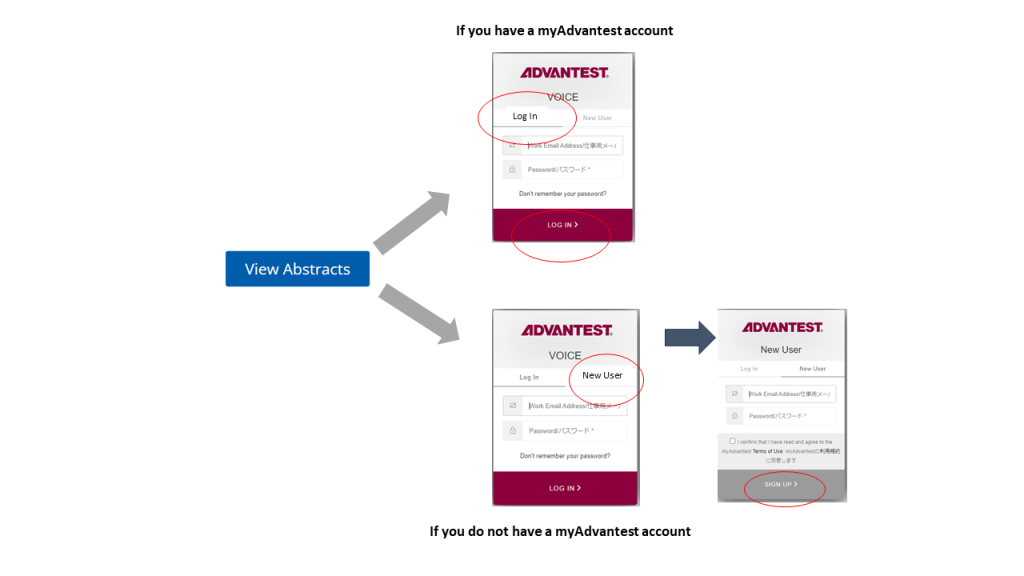

- To view all abstract titles, author and content click on the button below to be redirected to myAdvantest.

- Login with your myAdvantest credentials or sign up for an account clicking the "New User" tab on the myAdvantest portal.

- New accounts will be verified within 3-5 business days, at which time you will get full access to VOICE paper abstracts.

TECHNICAL TRACKS & TITLES

Artificial Intelligence

- Leveraging Generative AI for Domain-Specific Knowledge Retrieval and Interaction

- Predictive Test Selection for Silicon at System Level Using Machine Learning and Cloud services.

- Advanced Dynamic Binning Solution for Multi-Core Chips

- Streamlining Concurrent Test Flow Testing of AI Chips

5G/Millimeter Wave

- Accurate RF Power Measurements with SmarTest

- Low-Cost, High-Efficiency ATE Test Solution for 5G RedCap Devices

- Maximizing Throughput with Next-Generation RF Instrument on the V93000 Platform

- HRP-UWB PHY Modulated Testing

- HRP-UWB Production Testing from WSRF to WSRF 20ex

Automotive, Power, Analog and Mixed Signal

- Test Solution for a High-Performance 256-Channel 20-Bit ADC Chip

- Ultra-High-Precision DAC Test Solution at µV level with DC Scale AVI64

- High-Multi-Site, High-Voltage Test Solution for Power SiP Devices

- Using Wave Scale MX to Simplify Automotive Sensor Chip Test Circuits

- Low-Cost Solution for Testing High-Accuracy DAC/ADC Using XPS256

- Implementing Wave Scale MX_HR in a 16-Site High-Fidelity Smart Audio Testing Solution

- SmarTest 8 Characterization Library Best Practices for ADAS Applications

- A High-Efficiency Smart TV Chip Test Solution on V93000 EXA Scale

- Low-Cost Charger Device Test Solution by using XPS128+HV on EXA Scale

- Best Practices Using Wave Scale MX for Current Sourcing Test

- XPS256 AWG and DGT with Xtreme Regulation Technology on Mixed-Signal Devices

- Common Building Blocks on V93000 for Media SoC Analog Test

- Using Pin Scale 5000 C-DAC for Low-Cost Solution in High-Volume MCU Manufacturing

- Automotive System Basis Chip CAN-FD Transceiver Test Solutions on V93000

- Optimizing Test Time for Automotive Airbag Devices Using SmarTest 8

- Accurate Differential Voltage Forcing Solution onto High-Reference Voltage with V93000

- Advanced Solution for SmarTest 8 PAC Complex Trimming and Comparator

- Testing a High-Cell-Count BMS Device Using a Hybrid Cell Meter Approach

High Performance Digital

- Pin Scale Multi-Level Serial (PS MLS) Re-Timed Loopback Development

- Enabling Future HPC Device Roadmap Using XHC32 Instrument

- Boosting Scan-over-HSIO Implementation to 33Gbps with Pin Scale Multilevel Serial

- Practical Change Period Implementation for Scan Test Patterns with PS5000 CT Immediate + SmarTest8

- Strategies for Preventing Burned Probes on the V93000 EXA Scale Platform

- Deep Learning Application for ADAS Testing with proteanTec at Exascale

- Silicon Photonics Optical Control Library (OCL)

- Revolutionizing DDR5 DIMM Chipset Testing: A New Era of Speed and Precision

- Flow-Level CCT Solution for HPC Chips

- PinScale 5000 Protocol Link in SmarTest 8 Using Digital Pins as Embedded Protocol Interface

- Challenges of Migrating a High-Performance Compute Application from XPS256 to XHC32

- Beyond X5R? Exploring Thermal Effects of High Temperature Testing

- High-Power Computation DUT Board Design and Test Program Adaptation Techniques for Migrating from UHC4T to XHC32

- Greatly Enhanced Protocol Support Via New PS5000 Protocol Link Feature

Factory Automation

- Best Practices for Improving OEE of V93000 Final Test Cell in Production

Hardware & Software Design Integration

- Best Time-to-Quality Universal Inspection Solution Using SmarTest 8

- Wave Scale RF-20ex Single-Tone Measurement Throughput Study

- Using Match Loop Features on Pin Scale 5000 to Develop AC Timing Measurements for New Protocols

- Best Practices for DC Scale UHC4T to XHC32 Migration

- Enhance Search Speed by Utilizing Embedded CoGo in SmarTest 8

- Test Specification Management for Automatic Test Program Generation on SmarTest 8

Test Methodologies

- Cross Correlation EVM Method: Introduction and Implementation with V93000 Wave Scale RF

- Addressing High-Performance Analog Interface ADDA testing for Wi-Fi 7 Router

- V93000 EXA Scale with Duo Interface Boosts AP Device Testing

- Test Cost Optimization in SiP Product Development Through Efficient V93000 Concurrent Testing

- V93000 EXA Scale Latch-Up Testing of High-Power Devices

- Test Challenges and Low-Cost Test Solutions for PMIC Development on V93000 EXA Scale

- TestStream: Software Framework for Automated Test Setup, Execution and Postprocessing

- Optimizing Multiple Clock Setup in SmarTest 8 for Optimal Throughput

- Vmin to the Max: A New Approach to Single-Sequencer Run Searching

- Boosting Efficiency and Security in Test Development with Podman on RHEL9

- Power Integrity Design and Post-Verification for XPS256

- Implementing TestFlow per Site in SmarTest 8

- Improving DDR Yield by Performing Optimization on Input/Output Settings

- Streamlining SmarTest 8 Offline Result Emulation with Simplified Configuration Through Modular CSV Files

- Optimizing SmarTest 8 Specification Search for Test Time Reduction and Granular Result Precision

- Lessons from Migrating to the V93000: 4.25X Faster, 2X Increased Parallelism

- Best Practices of Test Time Reduction and Memory Optimization for GPU Test Library on SmarTest8

- Automating Testing Processes: Integrating Git, SSF API, ORE API, and SmartCI on Jenkins

- Automated Digital-Pin Resource Sharing and Site Sequencing Handled by SmarTest 8

- Integrating SSN in Production Testing: Benefits and Implementation on smartTest8

- Designing a Scalable Loadboard for Efficient Power Supply Management

- A Scalable and Interactive Solution for Dynamic Shmoo Testing on HPC Devices in SmarTest 8

- Streamlined Shmoo Characterization Solution for Efficient GPU Pattern Bring-Up in SmarTest 8

- Best Practices for Transitioning Test Method Libraries from SmartTest 7 to SmartTest 8

- Optimizing DUT Testing Efficiency through Integration of RF and Communication Interface Testing

- Test Program Development Framework for Reduced Time-to-Market

- Leveraging On-Chip Monitoring and Machine Learning Algorithms Using External Libraries in SmarTest 8

- Synopsys Streaming Fabric with Advantest V93000 ATE Support

- SmarTest 8 Current and Voltage Profiling Techniques: Strategies, Use Cases and Best Practices

- A Novel Approach to Functional Test Using SiConic without Requiring PSS

- Case Study: Fail Log Feedback to ATPG Scan Diagnostics and Solutions Fixing Cycle information

- Left-Shifting Functional Validation to Wafer Sort

- Vector Memory Toolset for SmarTest 8

- Real-Time UART Data Streaming and Logging on ATE for Enhanced Failure Analysis

- Enhancing Reliability in Testing: Proactive Detection of Hot Switching and Relay Failures

- Development of Serial Buses in SmarTest 8 Using Utility Lines with Protocol Access Comparison

- Parametric Testing of HSIO Pads Without DC Access

- Test Power Debug and Characterization with SmartShell DC Profiling

- Minimizing Test-Time Overhead When Using Slow Digital Protocols on EXA Scale PS5000

T2000

- SiPM (LiDAR) Measurement Solution on T2000

- Toolchain to Convert Schematic Information for Use with T2000 IPSE Test Systems

- Investigation of the Voltage Dependency of Standard Capacitors Using the Advantest T2000 IPSE

- Efficiency Improvement Using RDK Assistant

- Advanced Accuracy in BMIC Chip Testing with High-Power Stack Integration

- Optimized Cost-Reduction Test Solutions for MCU, Sensor, and Driver ICs Using T2000-AIR

Hot Topics

- New Bluetooth Channel Sounding Production Testing on V93000

- Simplifying SmarTest 8 ATPG Flows for Enhanced Generality and Efficiency

- ACS Nexus Enables ACS RTDI to Empower Data Feedforward/Feedback in Semiconductor Production

- Planning for Vector Memory Usage in the Chiplet Era

- Testing SparkLink Low Energy Access Mode on V93000

- Testing Challenges and Low-Cost Test Solutions for 6nm Process RTOS Smartwatch Device

- 5G RedCap Test Solution on V93000

- From 200 MHz to 2 GHz – An Answer to UWB Test Challenges

- Best Practice for Wi-Fi 6 Router Test Solution on the V93000 WSRF Platform

- Best Practices for Testing 800G DSPs on the V93000 Platform